Professional Experience

Broccoli [webbroccolimicro.io]

Founder

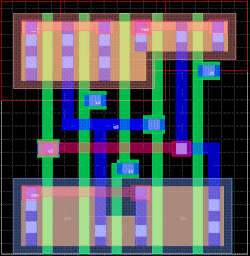

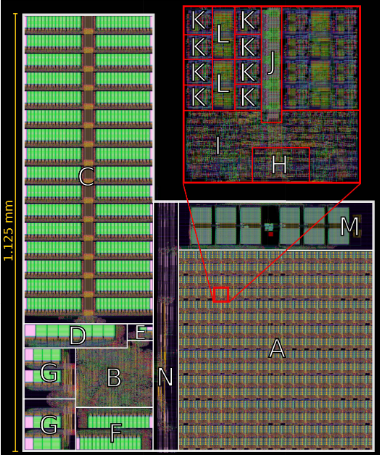

Developed EDA flow for asynchronous chips, called Loom (see projects). Built a lecture series on asynchronous circuit design (see teaching), and taught this lecture series twice to small groups. Created many circuit modules required for a reconfigurable array chip architecture. Formed business, submitted proposals to NSF Seed Fund, Activate, NASA SBIR, and DIU, and whitepapers for other BAAs and granting opportunities. Created financial and manufacturing models for chip tapeout. Continuous outreach to local hard-tech communities.

Bloomington, IN

Dec 2021 - Current

Siden

Senior Software Engineer

Increased the scalability of the content delivery scheduling system by two orders of magnitude. Designed and implemented the event processing system including real-time evaluation of 20 different KPIs and management of dataflow for analytics. Organized and mediated review of five major system architecture specifications as head of the Architecture Review Board. These systems formed the fundamental backbone of the final product.

Remote

Jan 2021 - Feb 2022

Software Engineer

Developed the emoji picker in 2018 for chat.google.com including front and back end design. Designed and implemented a complete development environment and circuit library for self-timed circuits in 2016 with automatic test generation and mixed-signal simulation.